Current Control Simulation by LTspice

Introduction

When controlling a motor or connecting to the grid by a voltage-source inverter (VSI), current control*1 is necessary. Nowadays, it must be rare to do the job with an analog circuit using operational amplifiers, etc.*2 whereas microcontrollers, DSPs (digital signal processors), and/or FPGAs (field-programmable gate arrays) are chosen as the control hardware. In this case, the system becomes discrete-time where the control computation routine is called cyclically every sampling period like functions called by a timer interruption, etc. A dead time is then introduced for time T so that the control gain design is an issue to ensure stability. Moreover, in the VSI control, PWM converts the output voltage reference to a pulse pattern which has the same average value.

I have learned power conversion circuits and their control. Yet, my understanding to the current control was really ambiguous. Hence, I try to perform the following two comparisons using LTspice XVII and my own control system library, Contraille.

- Continous-time (analog) vs. discrete-time (digital) controls

- Arbitrary vs. pulse-width-modulated voltage sources

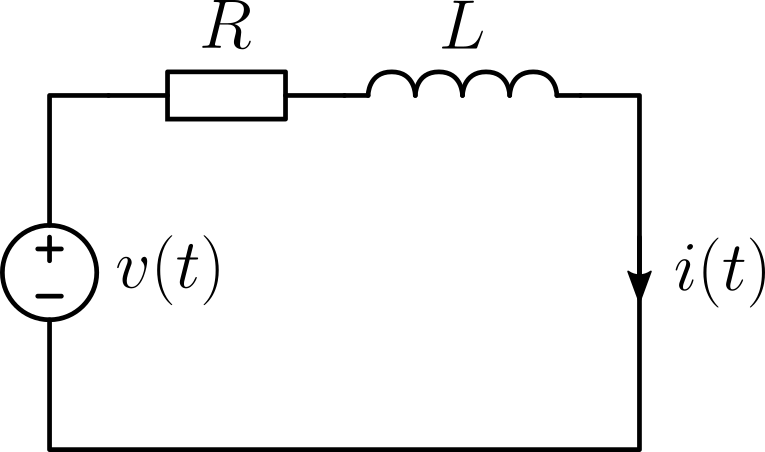

The object here is a simple RL circuit.

The voltage v(t) is adjusted so that the current i(t) has a desired value or waveform. In this case, the "controlled variable" is i(t) whereas v(t) is called the "manipulated variable" although this term seems not widely used. Just in case, t is time and both v(t) and i(t) become a function dependent on time t.

DISCLAIMER: This entry may contain technical errors!

My smattering knowledge heard from others

It is often said (?) that when R = 0 Ω and the sampling period is T, the current i(t) does not overshoot by setting the current control proportional gain KP to satisfy:

This is stated in, e.g., Refs. *3 and *4. However, it could be necessary to pay one's own effort to understand it. So, I will try to play with block diagrams and equations.

Let's see a simulation example.

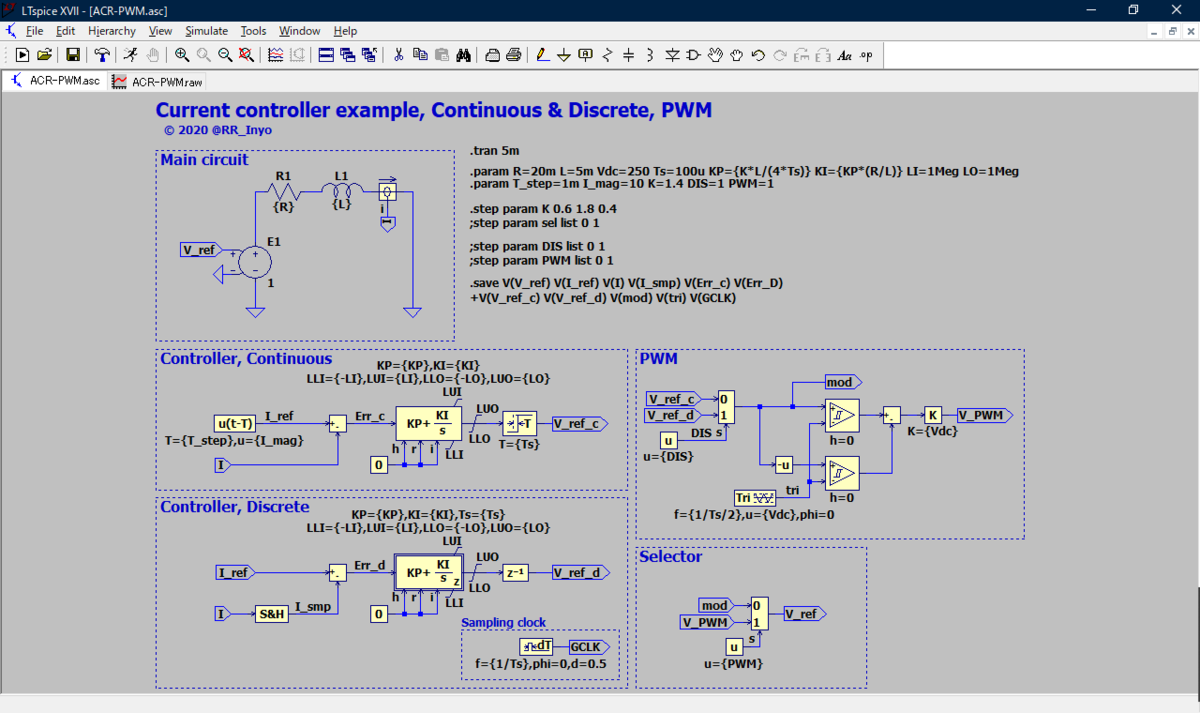

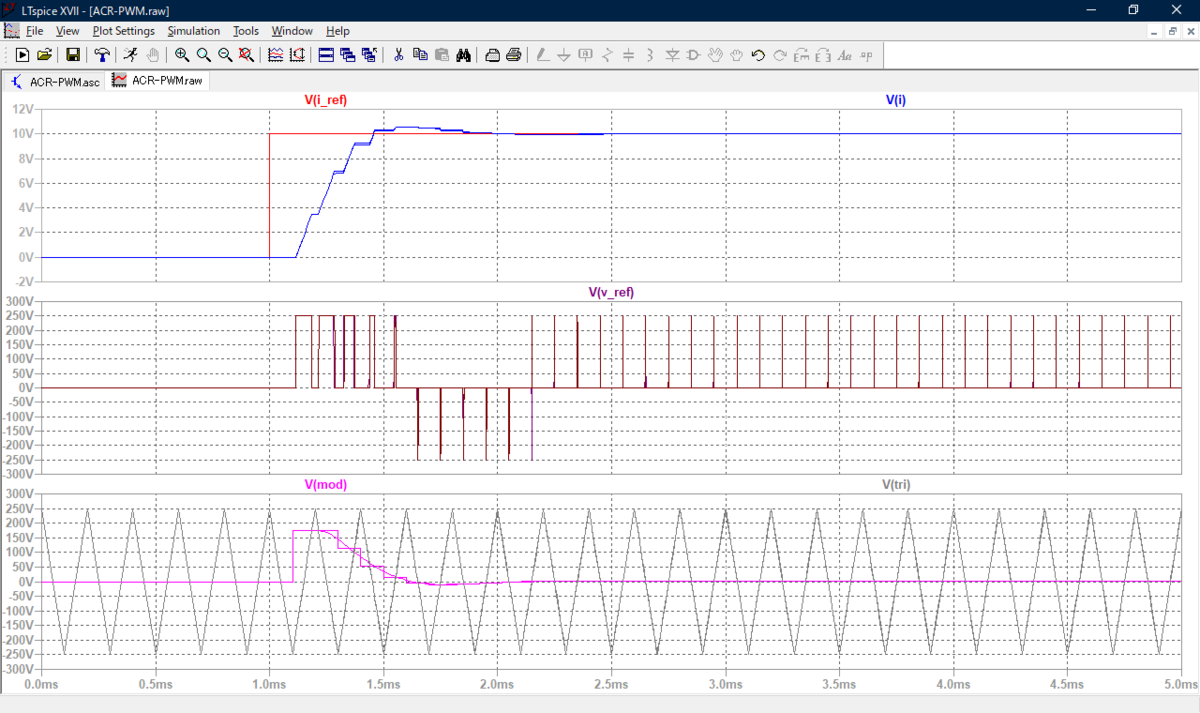

A schematic shown in Fig. 2 has been created using LTspice XVII and my own control system library, Contraille. There are two controllers, the continuous- and the discrete-time controllers, in parallel, and you can select one by a multiplexer. In addition, one more multiplexer can select whether the output signal of the controller goes directly to the voltage-dependent voltage source E1, or is pulse-width-modulated before going to E1.

This is just an example, but the circuit and control parameters are summerized in Table I.

| Paeameter | Value |

|---|---|

| Resistor, R | 20 mΩ |

| Inductor, L | 5 mH |

| Sampling period | 100 μs |

| Proportional gain, KP | |

| Integral gain KI |

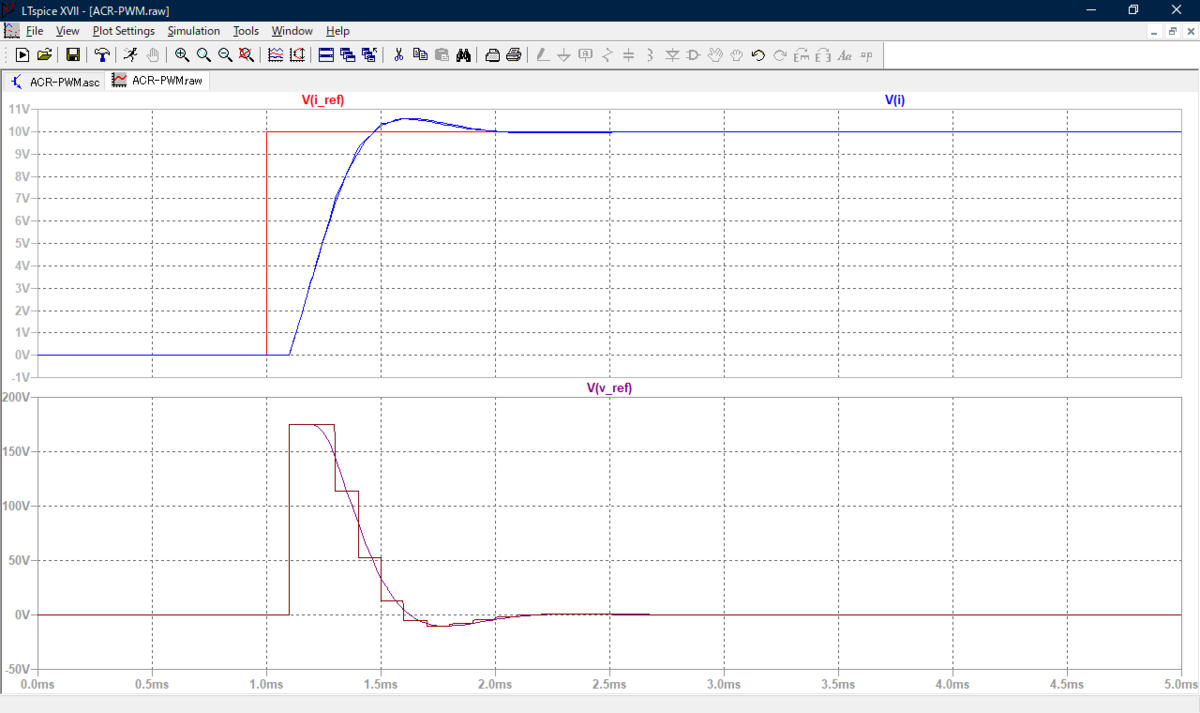

The proportional gain has a parameter K, which is changed to be K = 0.6, 1.0, 1.4, and 1.8, by .step param command of LTspice.

When K = 1, KP = L / (4 T) as in (1).

As can be seen in Fig. 3, when K = 1, the current i(t) has no overshoot.

Simple block diagram in continuous time

Fig. 4 shows the simplest block diagram in the s-domain, applying a PI (proportional and integral) controller, the simplest block diagram without considering the dead time.

If you set the proportional gain KP and the integral gain KI to satisfy:

pole-zero cancellation occurs, making Go(s) be:

Then, the closed-loop transfer function Gc(s) is a first-order delay with ωn = KP / L as expressed like:

The problem here is how the proportional gain KP should be set. As mentioned above, if setting KP = L / (4 T), which is the border to have no overshoot,

This is a first-order delay of ωn = 1 / (4 T). For example, if T = 100 μs, ωn = 2,500 rad/s.

In reality, however, a dead time accompanying the computational time and frequency characteristics of the current sensor matter so that it is necessary to check the gain and phase margins, (which I would like to write in another entry.)

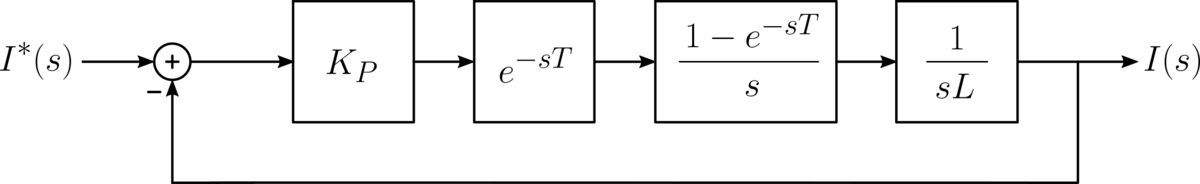

Block diagram in discrete-time control

As far as I see some textbooks, they first express discrete-time control systems in the continuous-time s-domain. Let's begin with R = 0 Ω and KI = 0.

In Fig. 5, e−sT is a dead time for one sampling period and (1 − e−sT) / s is the transfer function of a zero-order hold. The open-loop transfer function Go(s) is derived from Fig. 5 as:

Converting this to the z-domain, you obtain:

The closed-loop transfer function Gc(z) can be written as:

Then, the characteristic roots of Gc are:

The overshoot does not happen when the characteristic roots are real. It means that the inside of square root in (10) is positive as follows:

This is the way to theoretically reach the conclusion of "My smattering knowledge heard from others" (although I do not fully understand how...😅).

Simulation results

Let me present other simulation results.

I will prepare and clean up my own control system library Contraille and make it available publicly!

[Updates while translating] I have uploaded Contraille in GitHub already. See below.

Updates: Moving-average filter to detected current signal

The continuous-time controller in Fig. 2 compared the detected current signal directly with the current reference. Meanwhile, the discrete-time controller needed to sample and hold the current signal i(t) after detection. I guessed that the difference between continuous- and discrete-time controller in Figs. 3 and 6-8 was in this point.

Textbooks of digital control and z-transform say transfer function of sample and hold, GSH(s), can approximately be written as:

This is completely the same as that of the moving average filter (MAF). Hence, why don't we add a MAF to the detected current signal i(t) in the continuous-time controller and compare its behavior with that of the discrete-time controller again?

Let's set the current control proportional gain KP = 1.4 × L / (4 T) which will cause overshoot and compare the continuous- and discrete-time controllers.

Whoa! Waveforms of continuous- and discrete-time controllers almost perfectly coinside! Adding a MAF to the continuous-time controller has made the behaviors of the two controllers almost equal, whereas they were different in Figs. 3 and 6-8 despite the same proportional gain KP. In other words, discrete-time (digital) control, needing to perform sample and hold, automatically has a characteristics of MAF in the feedback loop. In addition, this coincidence does not depend on whether PWM is done or not.

Well, I had not been able to deeply grasp this kind of insight without doing hands-on myself.

Appendix

This is a translation to my original Japanese entry linked below:

*1:Sometimes current control is referred to as "ACR", but I guess this is a Japanese English.

*2:早川:「初めての自立移動ロボット制御シミュレーション」,トランジスタ技術,2020年7月号,pp. 71-86

*3:J. Tahara, H. Fujita, and H. Akagi, "Control and performance of a PWM eectifier with an FPGA-based current controller," IEEJ Technical Meeting on Semiconductor Power Converter, SPC-05-14, Jan. 2005, Osaka, pp. 33-38.

田原・藤田・赤木:「FPGAによる高速電流制御を適用したPWM整流器の動作特性」,電気学会半導体電力変換研究会資料SPC-05-14,pp. 33-38,2005年1月,大阪

*4:H. Akagi, E. H. Watanabe, and M. Aredes, Instantaneous Power Theory and Applications to Power Conditioning, Wiley, 2007